لینک دانلود و خرید پایین توضیحات

فرمت فایل word و قابل ویرایش و پرینت

تعداد صفحات: 22

فصل دوم

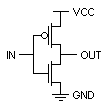

جبر بول و گیت های منطقی (Boolean alyebra)

اعمالی که در دستگاههای الکترونیکی و یا با کامپیوترها انجام می پذیرد از یک برنامه program پیروی می کند پاسخهای که به وضعیتهای متغیر یک برنامه داده می شود از یک منطق معین تبعیت می نمایند منطق علم استدلال یا علم نتیجه گیری از مفروضات است.

در علم Logic قوانین و اصولی وجود دارد که در آنها استنتاج صحیح و اصولی از دادهها انجام می گیرد.

عبارات منطقی بصورت سمپلها و معادلات نوشته می شود و ساده ترین سمبلها در این منطق درست یا نادرست و یا به عبارتی بسته یا بار بودن یک کلید است در هر حال خروجی می تواند نشان دهنده یک وضعیت باشد.

در سال 1854 ریاضی دان انگلیسی به نام جورج بول George Bole روابط منطقی را با استفاده از سیستم باینری به صورت یک سر فرمولهای ریاضی بیان نمود که شامل یک مجموعه از الگوها و تعدادی اصول می باشد که تشابهی با اصول جبر معمولی ندارد.

در سال 1938 نیز دانشمند دیگری به نام سی.ای. شانون یک جبر بول دو مقداری را به نام جبر سوئیچینگ معرفی نمود که در طراحی مدارات سوئیچینگ به کار گرفته می شود.

جبر بول نیز همانند هر سیستم ریاضی دارای یک فرضیات اولیه می باشد که از آنها قوانین و تئوری های مورد نظر را می توان نتیجه گرفت و به عنوان یک ساختار جبری معین بکار گرفت.

روابط و قوانین این جبر برای طراحی مدارات منطقی و سیستم های دیجیتالی مورد استفاده قرار می گیرد در جب بول فرض اصلی بر این است که دارای یک متغیر باینری هستیم که اگر x یک متغیر باینری باشد و اگر مقدار آن باشد در این صورت حتماً مقدارش برابر خواهد بود و اگر باشد حتماً خواهد بود و حالتی دیگری برای متغیر x متصور نیست این دو مقدار (1و0) به مقادیر صحت Trutr-valve و جدول مقادیر ارزشی 0 و 1 را جدول دستی می نامند.

قبل از بیان اصول و تئوری های عنوان شده در جبر بول با توجه به اصول مطرح شده بخش مجموعه ها قابل ذکر است که مجموعه S می تواند شامل عناصر مشخصی همانند A و B باشد در این صورت و میباشد یعنی A عضوی از S و B نیز عضوی از S است در این صورت می توان گفت عنصر N عضوی از S نمی باشد. یک مجموعه با تعداد مشخصی از عناصر تشکیل شده است لذا مجموعة عناصر را با یک جفت اکولاد نشان می دهند.

مجموعة اعداد طبیعی از 1 شروع می شود و هر عضو دیگر آن با افزودن یک واحد به عدد قبلی به دست می آید.

در این صورت عملگری که می تواند در این مجموعه صحیح باشد و موجب شود عناصر بدست آمده در مجموعه اعداد طبیعی قرار گیرد عملگرهای جمع و ضرب میباشد+ و نتیجه می توان گرفت یک عملگر زمانی بر روی عناصر یک مجموعه معتبر است که عنصر جدید به دست آمده حاصل از ضرب یا جمع دو عنصر از مجموعه مورد نظر در آن مجموعه قرار گیرد.

دانلود مقاله کامل درباره جبر بول و گیت های منطقی (Boolean alyebra